UNIST·미네소타주립대, 원자층증착법으로 초미세 반도체 전극 패턴 제작

실리콘 반도체칩 대체하는 초소형 반도체칩 기술 등에 응용가능

뷰어

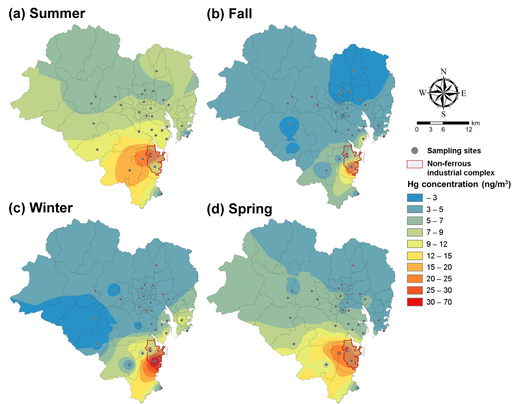

초미세 반도체 전극구조 제작 과정 및 2차원 소자 제작. /그림=UNIST

손톱만한 반도체칩 안에는 최대 수십억 개의 미세소자가 들어있다. 이 미세소자는 여러 층의 재료 속에 그려진 패턴 형태로 존재한다. 패턴 제조를 위해서는 빔으로 모양을 그리는 공정이 필요한데, 최근 국제 공동 연구진이 고가의 빔 공정이 필요 없는 초미세 패턴 제조 기술을 개발해 눈길을 끈다.

울산과학기술원(UNIST) 물리학과 남궁선 교수와 미국 미네소타주립대 연구진은 물질을 여러 번 얇게 입히는 공정(원자층증착법)만으로 반도체 패턴 제조가 가능한 기술을 개발했다고 24일 밝혔다.

빔 기반 기술보다 간편하고 저렴하며, 원자층을 입히는 횟수로 채널 폭(전극 간 간격)을 나노미터 단위로 바꿀 수 있다. 또 이 방식은 실리콘 대신 2차원 반도체 물질을 쓴 신개념 반도체 소자 제작에도 매우 유리하다.

연구팀은 이 기술을 이용해10㎚(나노미터, 10억분의 1m) 이하 채널을 갖는 초미세 ‘반도체 전극’과 2차원 반도체 소자(트랜지스터)를 제작했다. 금속(전극)-절연체-금속(전극) 순서로 기판위에 증착해 나노 갭(gap) 패턴을 만들고, 이를 기판에서 뜯어내 뒤집으면 절연층 두께만큼 전극 간 거리가 분리 된 전극 패턴이 완성된다. 전극 표면이 기판에서 바로 분리됐기 때문에 표면이 매우 매끈하다는 장점이 있다. 이 때문에 전극 위에 2차원 반도체 물질(이황화몰리브덴, 흑린 등)쌓아 소자(트랜지스터)를 만들기에 적합하다.

또 연구팀은 이를 트랜지스터 기반 광 검출기로도 응용했다. 초미세 트랜지스터 전극 사이의 강한 전기장이 빛에 의해 생성된 전하 입자들을 효과적으로 분리해 검출 성능을 향상시킬 수 있었다. 광 검출기는 빛을 전류(전하입자)의 형태로 검출하는 소자로 초고속 광통신 등에 필수적이다.

제1저자인 남궁 교수는 “기존의 반도체 공정 기술인 원자층증착법을 활용해 균일한 나노미터 단위의 전극 구조를 대량으로 생산할 수 있는 기술”이라며 “반도체 구조 소형화 및 초소형 광통신 모듈, 광학반도체칩 개발에 도움이 될 수 있을 것”이라고 기대했다.

이번 연구는 나노·재료 분야의 권위 학술지인 에이씨에스 나노(ACS Nano) 에 2월 24일자로 온라인 공개돼 정식출판을 앞두고 있다.

/울산=장지승 기자 [email protected]

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

![[울산소식]동서발전 노사, 산불 피해 성금 전달 등 : 네이트 뉴스](https://thumbnews.nateimg.co.kr/view610///news.nateimg.co.kr/orgImg/ns/2025/04/02/NISI20250402_0001808000_web.jpg)

![[울산소식]온양농협, 장학금 2000만원 전달 등 :: 공감언론 뉴시스 ::](https://img1.newsis.com/2025/02/28/NISI20250228_0001781082_web.jpg?rnd=20250228161600)